HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

# **FEATURES**

- HIGH INTERNAL DISSIPATION 125 Watts

- HIGH VOLTAGE, HIGH CURRENT 100V, 10A

- HIGH SLEW RATE 10V/µs

- 4 WIRE CURRENT LIMIT SENSING

- OPTIONAL BOOST VOLTAGE INPUTS

# **APPLICATIONS**

- LINEAR AND ROTARY MOTOR DRIVES

- YOKE/MAGNETIC FIELD EXCITATION

- PROGRAMMABLE POWER SUPPLIES TO ±45V

- INDUSTRIAL AUDIO

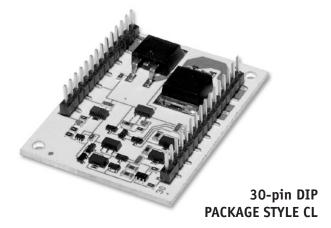

- PACKAGE OPTION DIP10 DUAL-IN-LINE

#### **DESCRIPTION**

The MP39 is a cost-effective high voltage MOSFET power operational amplifier constructed with surface mount components on a thermally conductive but electrically isolated substrate.

While the cost is low the MP39 offers many of the same features and performance specifications found in much more expensive hybrid power amplifiers.

The metal substrate allows the MP39 to dissipate power up to 125 watts and its power supply voltages can range up to +/- 50 Volts (100V total). Optional boost voltage inputs allow the small signal portion of the amplifier to operate at higher supply voltages than the high current output stage. The amplifier is then biased to achieve close linear swings to the supply rails at high current for extra efficient operation. External compensation tailors performance to the user needs. A four-wire sense technique allows current limiting without the need to consider internal or external mili-ohm parasitic resistance in the output line. An Iq pin is available which can be used to shut off the guiescent current in the output stage. The output stage then operates class C and lowers quiescent power dissipation. This is useful in applications where output crossover distortion is not important.

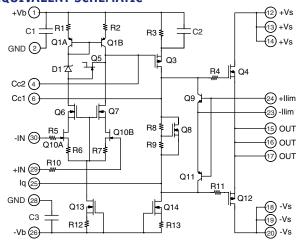

# **EQUIVALENT SCHEMATIC**

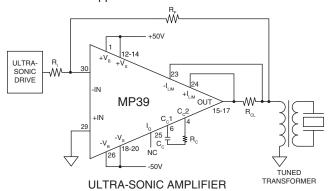

# **TYPICAL APPLICATION REF: APPLICATION NOTE 25**

The high power bandwidth and high voltage output of the MP39 allows driving ultra-sonic transducers via a resonant circuit including the transducer and a matching transformer. The load circuit appears resistive to the MP39.

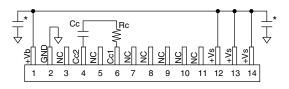

## **EXTERNAL CONNECTIONS**

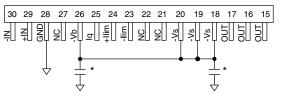

#### COMPONENT SIDE VIEW

#### \* SEE "BYPASSING" PARAGRAPH Phase Compensation

|      | i nace compensation |       |

|------|---------------------|-------|

| Gain | Cc                  | Rc    |

| 1    | 470pF               | 100Ω  |

| ≥ 3  | 220pF               | Short |

| ≥ 10 | 100pF               | Short |

## **ABSOLUTE MAXIMUM RATINGS**

SUPPLY VOLTAGE,  $+V_S$  to  $-V_S$ 100V **BOOST VOLTAGE**  $\pm V_s \pm 20V$ OUTPUT CURRENT, within SOA 25Å POWER DISSIPATION, internal 125W INPUT VOLTAGE, differential ±20V ±V<sub>B</sub> 200°C INPUT VOLTAGE, common mode TEMPERATURE, pin solder - 10s TEMPERATURE, junction<sup>2</sup> 175°C TEMPERATURE, storage -40 to +105°C OPERATING TEMPERATURE RANGE, case -40 to +85°C

## **SPECIFICATIONS**

|                                                                                                                                                                   |                                                                                                                                                                                                           | MP39                                                     |                                                                 |                 | MP39A |           |             |                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------|-----------------|-------|-----------|-------------|-------------------------------------------|

| PARAMETER                                                                                                                                                         | TEST CONDITIONS 1                                                                                                                                                                                         | MIN                                                      | TYP                                                             | MAX             | MIN   | TYP       | MAX         | UNITS                                     |

| INPUT OFFSET VOLTAGE, initial OFFSET VOLTAGE, vs. temperature OFFSET VOLTAGE, vs. supply OFFSET VOLTAGE, vs. power BIAS CURRENT, initial BIAS CURRENT, vs. supply | Full temperature range Full temperature range                                                                                                                                                             |                                                          | 5<br>30<br>15<br>30<br>10                                       | 10<br>50<br>200 |       | * * * * * | 3 *         | mV<br>μV/°C<br>μV/V<br>μV/W<br>pA         |

| OFFSET CURRENT, initial INPUT IMPEDANCE, DC INPUT CAPACITANCE COMMON MODE VOLTAGE RANGE COMMON MODE REJECTION, DC INPUT NOISE                                     | Full temperature range Full temp, range, $V_{\rm CM}=\pm20V$ 100kHz BW, $R_{\rm S}=1{\rm K}\Omega$                                                                                                        | ±V <sub>B</sub> ∓15<br>86                                | 10<br>10 <sup>10</sup><br>20<br>±V <sub>B</sub> ∓12<br>98<br>10 | 50              | *     | * * * * * | 30          | pA/V<br>pA<br>Ω<br>pF<br>V<br>dB<br>µVrms |

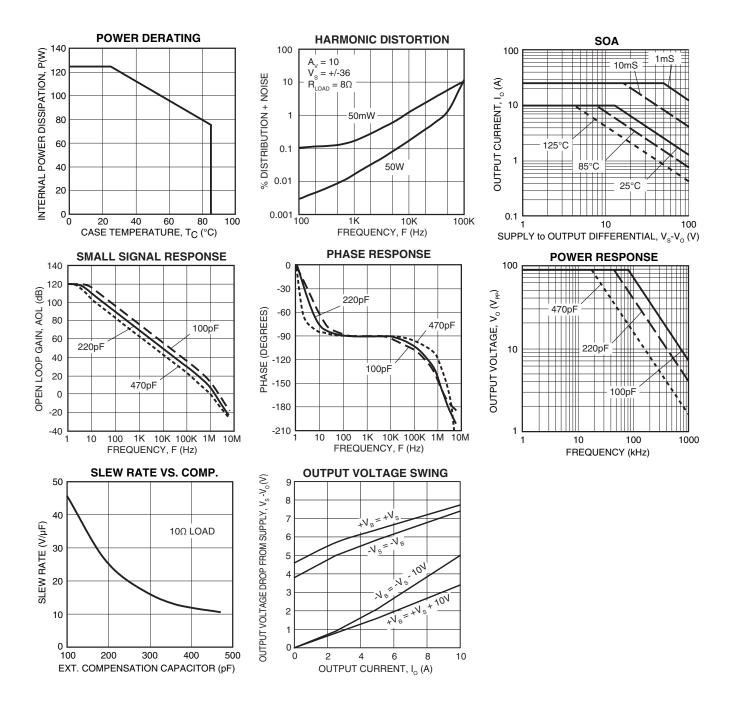

| GAIN OPEN LOOP, @15Hz GAIN BANDWIDTH PRODUCT POWER BANDWIDTH                                                                                                      | Full temperature range, $C_c = 100pF$<br>$I_o=10A$<br>$R_L=10\Omega$ , $V_O=90V$ p-p<br>$C_C=100pF$                                                                                                       | 94                                                       | 113<br>2<br>40                                                  |                 | *     | * *       |             | db<br>MHz<br>kHz                          |

| PHASE MARGIN                                                                                                                                                      | Full temperature range                                                                                                                                                                                    |                                                          | 60                                                              |                 |       | *         |             | 0                                         |

| OUTPUT VOLTAGE SWING VOLTAGE SWING SETTLING TIME to .1% SLEW RATE CAPACITIVE LOAD RESISTANCE CURRENT, CONTINUOUS                                                  | $\begin{split} I_o &= 10A \\ \pm V_B &= \pm V_S \pm 10V, \ I_o = 10A \\ A_v &= +1,10V \ \text{step}, \ R_L = 4\Omega \\ A_v &= -10, \ C_c = 100pF \\ Full \ temperature \ range, \ A_v &= +1 \end{split}$ | ±V <sub>s</sub> ∓8.8<br>±V <sub>s</sub> ∓6.8<br>10<br>10 | ±V <sub>s</sub> ∓6.0<br>±V <sub>s</sub> ∓1.1<br>2.5             | 10              | * * * | * * *     | 11          | V<br>V<br>μs<br>V/μs<br>nF<br>Ω<br>A      |

| POWER SUPPLY VOLTAGE CURRENT, quiescent, boost supply CURRENT, quiescent, total                                                                                   | Full temperature range                                                                                                                                                                                    | ±15                                                      | ±40                                                             | ±50<br>22<br>26 | *     | *         | *<br>*<br>* | V<br>mA<br>mA                             |

| THERMAL RESISTANCE, AC, junction to case <sup>3</sup> RESISTANCE, DC, junction to case RESISTANCE <sup>4</sup> , junction to air TEMPERATURE RANGE, case          | Full temperature range, F>60Hz<br>Full temperature range, F<60Hz<br>Full temperature range<br>Meets full range specification                                                                              | -40                                                      | 12                                                              | .9<br>1.2<br>85 | *     | *         | * *         | °C/W<br>°C/W<br>°C/W                      |

# NOTES: \*

- The specification of MP39A is identical to the specification for MP39 in applicable column to the left.

- 1. Unless otherwise noted: T $_{\text{C}}$  = 25°C, R $_{\text{C}}$  = 100 $\Omega$ , C $_{\text{C}}$  = 470pF. DC input specifications are  $\pm$  value given. Power supply voltage is typical rating.  $\pm V_{R} = \pm V_{S}$ .

- Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF. For guidance, refer to the heatsink data sheet.

- Rating applies if the output current alternates between both output transistors at a rate faster than 60 Hz. 3.

- The MP39 must be used with a heat sink or the quiescent power may drive the unit to junction temperatures higher than 175°C.

CAUTION The MP39 is constructed from MOSFET transistors. ESD handling procedures must be observed.

## **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexmicrotech.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit; heat sink selection; Apex's complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

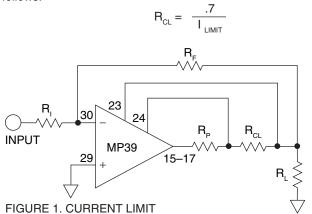

#### **CURRENT LIMIT**

The two current limit sense lines are to be connected directly across the current limit sense resistor. For the current limit to work correctly pin 24 must be connected to the amplifier output side and pin 23 connected to the load side of the current limit resistor,  $R_{\rm CI}$ , as shown in Figure 1. This connection will bypass any parasitic resistances, Rp, formed by sockets and solder joints as well as internal amplifier losses. The current limiting resistor may not be placed anywhere in the output circuit except where shown in Figure 1.

The value of the current limit resistor can be calculated as follows:

# **BOOST OPERATION**

With the V<sub>R</sub> feature the small signal stages of the amplifier are operated at higher supply voltages than the amplifier's high current output stage. +V<sub>s</sub> (pins 12-14) and -V<sub>s</sub> (pins 18-20) are connected to the high current output stage. An additional 10V on the V<sub>B</sub> pins is sufficient to allow the small signal stages to drive the output transistors into saturation and improve the output voltage swing for extra efficient operation when required. When close swing to the supply rails is not required the +V<sub>B</sub> and  $+V_s$  pins must be strapped together as well as the  $-V_B$  and  $-V_s$  pins. The boost voltage pins must not be at a voltage lower than the V<sub>s</sub> pins.

#### **BYPASSING**

Proper bypassing of the power supply pins is crucial for proper operation. Bypass the ±Vs pins with a aluminum electrolytic capacitor with a value of at least 10µF per amp of expected output current. In addition a .47µF to 1µF ceramic capacitor should be placed in parallel with each aluminum electrolytic capacitor. Both of these capacitors have to be placed as close to the power supply pins as physically possible. If not connected to the Vs pins (See BOOST OPERATION) the V<sub>p</sub> pins should also be bypassed with a .47µF to 1µF ceramic capacitor.

#### USING THE IQ PIN FUNCTION

Pin 25 (Ia) can be tied to pin 6 (Cc1) to eliminate the class AB biasing current from the output stage. Typically this would remove 1-4 mA of quiescent current. The resulting decrease in quiescent power dissipation may be important in some applications. Note that implementing this option will raise the output impedance of the amplifier and increase crossover distortion as well.

# COMPENSATION

The external compensation components C<sub>c</sub> and R<sub>c</sub> are connected to pins 4 and 6. Unity gain stability can be achieved at any compensation capacitance greater than 470 pF with at least 60 degrees of phase margin. At higher gains more phase shift can be tolerated in most designs and the compensation capacitance can accordingly be reduced, resulting in higher bandwidth and slew rate.

#### APPLICATION REFERENCES

For additional technical information please refer to the following application notes.

AN 1 **General Operating Considerations**

**AN 11** Thermal Techniques

**AN 38** Loop Stability with Reactive Loads